# LECTURES NOTES ON DIGITALELECTRIONICS AND MICROPROCESSOR

# GOVT.POLYTECHNIC,BHADRAK

# **PREPARED BY** TAPAN KUMAR DAS

# DEPARTMENT OF ELECTRICAL ENGINEERING Government Polytechnic, Bhadrak

#### BASICSOFDIGITALELECTRONICS

The branch of electronics that deals with digital data in the form of codes. There areonly two codes in digital electronics, and they are 0 and 1. 0 is considered to be lowlogic while 1 is considered to be high logic.

Digital Electronicscan also be defined as the circuit which deals with Digital Signal is knows as Digital Electronics

#### **AdvantagesOfDigitalElectronics**

- a. DigitalElectroniccircuitsarerelativelyeasytodesign.

- b. Ithashigherprecisionrateintermsofaccuracy.

- c. Transmittedsignalsarenotlostoverlongdistance.

- d. DigitalSignalscanbestoredeasily.

- e. Digital Electronics is more immune to 'error' and 'noise' than analog. But in case of high-speed designs, a small noise can induce error in the signal.

- f. ThevoltageatanypointinaDigitalCircuitcanbeeitherhighorlow;hence there is less chance of confusion.

- *g.* DigitalCircuitshavetheflexibilitythatcanchangethefunctionalityofdigital circuits by making changes in software instead of changing actual circuit.

#### **DisadvantagesofDigitalElectronics**

- a. The real world is analog in nature, all quantities such as light, temperature, soundetc.DigitalSystemsisrequiredtotranslateacontinuoussignaltodiscrete which leads to small quantization errors. To reduce quantization errors a large amount of data needs to be stored in Digital Circuit.

- b. DigitalCircuitsoperateonlywithdigitalsignalshence,encodersanddecoders are required for the process. This increases the cost of equipment.

#### NumberSystem

A digital system can understand positional number system only where there are a few symbols called digits and these symbols represent different values depending on the position they occupy in the number.

Avalueofeachdigitinanumbercanbedeterminedusing

- a. Thedigit

- b. Thepositionofthedigit inthenumber

- c. The base of the number system (where base is defined as the total number of digits available in the number system).

#### TypenumberSystem

- 1. DecimalNumberSystem

- 2. BinaryNumberSystem

- 3. OctalNumberSystem

- 4. HexadecimalNumberSystem

### DecimalNumberSystem

Thenumbersystemthatweuseinourday-to-daylifeisthedecimalnumbersystem The decimal number system contains ten digits from 0 to 9.(0,1,2,3,4,5,6,7,8,&9) Base=10 Thepositioninthedecimalnumbersystemspecifiesthepowerofthebase(10).

## Example

Mathematically, we can write it as

$2541 = (2 \times 1000) + (5 \times 100) + (4 \times 10) + (1 \times 1)$  $= (2 \times 10^{3}) + (5 \times 10^{2}) + (4 \times 10^{1}) + (1 \times 10^{0})$ = 2541

### BinaryNumberSystem

Generally, abinary number system is used in the digital computers. In this number system, it carries only two digits, either 0 or 1

Thebinarynumbersystemcontains2digitsfrom0&1 Base=10

The position in the binary numbers ystems pecifies the power of the base (2) Mathematically,

we can write it as

```

1101.011=(1\times2^{3})+(1\times2^{2})+(0\times2^{1})+(1\times2^{0})+(0\times2^{-1})+(1\times2^{-2})+(1\times2^{-3})

OctalNumberSystem

```

Theoctalnumbersystemcontains8digitsfrom0to7(i.e.0,1,2,3,4,5,6&7) Base=8

The position in the octal number system specifies the power of the base (8) Mathematically,

we can write it as

12570=(1×8<sup>4</sup>)+(2×8<sup>3</sup>)+(5×8<sup>2</sup>)+(7×8<sup>1</sup>)+(0×8<sup>0</sup>) **HexadecimalNumberSystem** Uses10digitsand6letters,0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F.

Lettersrepresentsnumbersstartingfrom10.A=10,B=11,C=12,D=13,E=14,F=15. Base =16

The position in the Hexa decimal Number System number system specifies the power of the

base (8)

Mathematically, we can write it as

$19FDE_{16}=(1\times16^{4})+(9\times16^{3})+(F\times16^{2})+(D\times16^{1})+(E\times16^{0})$

#### NumberSystemandBaseConversions

ElectronicandDigitalsystemsmayuseavarietyofdifferentnumbersystems, (e.g. Decimal, Hexadecimal, Octal, Binary).

AnumberNinbaseorradixbcanbewrittenas:

(N)b=dn-1dn-2-----d1d0.d-1d-2----- d-m

Intheabove, dn-1tod0istheintegerpart, thenfollows aradixpoint, and then

d-1 to d-m is the fractional part.

dn-1=Mostsignificantbit(MSB) d-

m = Least significant bit (LSB)

| Base | Representation |

|------|----------------|

| 2    | Binary         |

| 8    | Octal          |

| 10   | Decimal        |

| 16   | Hexadecimal    |

# 1. DecimaltoBinary

Convert(34.25)<sub>10</sub>toBinaryequivalent

Step1:Dividethenumber34anditssuccessivequotientswithbase2.

| 2)34 | Remainder |

|------|-----------|

| 2)17 | 0 +       |

| 2) 8 | 1         |

| 2 4  | 0         |

| 2) 2 | 0         |

| 2) 1 | 0         |

| 0    | 1         |

#### Step 2:

Now, perform the multiplication of 0.25 and successive fraction with base 2.

| Operation | Result | carry |

|-----------|--------|-------|

| 0.25×2    | 0.50   | 0     |

| 0.50×2    | 0      | 1     |

$(0.25)_{10} = (.01)_2$

FinalResultis

(??.??)22=(????????)2

## 2. BinarytoDecimal

```

Convert(1010.01)2toequivalentDecimalNo.

```

```

(1010.01)_2 = 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 0 \times 2^0 + 0 \times 2^{-1} + 1 \times 2^{-2} = 8 + 0 + 2 + 0 + 0 + 0.25 = 10.25

```

=(10.25)10

# 3. DecimaltoOctal

Convert(86)<sub>10</sub>toOctalequivalent **Step1:**Dividethenumber34anditssuccessivequotientswithbase8.

| 8 <u>)86</u> | Remainder |

|--------------|-----------|

| 8)10         | 6 🛉       |

| 8) 1         | 2         |

| 0            | 1         |

## Step2:

Now perform the multiplication of 0.35 and successive fraction with base 8.

| Operation | Result | carry |

|-----------|--------|-------|

| 0.35X8    | 2.8    | 2     |

| 0.8X8     | 6.4    | 6     |

| 0.4X8     | 3.2    | 3     |

| 0.3X8     | 2.4    | 2     |

## (0.35)10=(2632)8

So, the octal number of the decimal number 86.35 is 126.2632

### 4. OctaltoDecimal

$(12.2)_8$ 1x8<sup>1</sup>+2x8<sup>0</sup>+2x8<sup>-1</sup>=8+2+0.25=10.25 (12.2)<sub>8</sub>=(10.25)<sub>10</sub>

# 5. HexadecimaltoBinary

To convert from Hexadecimal to Binary, write the 4-bit binary equivalent of hexadecimal.

| Binary equivalent | Hexadecimal |

|-------------------|-------------|

| 0000              | 0           |

| 0001              | 1           |

| 0010              | 2           |

| 0011              | 3           |

| 0100              | 4           |

| 0101              | 5           |

| 0110              | 6           |

| 0111              | 7           |

| 1000              | 8           |

| 1001              | 9           |

| 1010              | А           |

| 1011              | В           |

| 1100              | С           |

| 1101              | D           |

| 1110              | E           |

| 1111              | F           |

# Example

(3A)16=(00111010)2

## 6. BinarytoHexadecimal

ToconvertfromBinarytoHexadecimal,startgroupingthebitsingroupsof4from the rightend and write the equivalent hexadecimal for the 4-bit binary. Add extra 0'son the left to adjust the groups.

1111011011 <u>001111011011</u> (001111011011)2=(3DB)<sub>16</sub>

## 7. Hexa-decimaltoDecimalConversion

The process of converting hexadecimal to decimal is the same as binary to decimal. The process starts from multiplying the digits of hexadecimal numbers with its corresponding positional weights. And lastly, we add all those products.

```

Example1:(152A.25)<sub>16</sub>

```

$(152A.25)_{16} = (1 \times 16^3) + (5 \times 16^2) + (2 \times 16^1) + (A \times 16^0) + (2 \times 16^{-1}) + (5 \times 16^{-2})$ = 5418.14453125

#### 8. DecimaltoHexadecimal

|      |      | Rema | ainder |

|------|------|------|--------|

| 16)2 | 2861 | Dec. | Hex.   |

| 16)  | 178  | 13   | Dţ     |

| 16)  | 11   | 2    | 2      |

|      | 0    | 11   | в      |

?????**=**??????

#### Binaryaddition, subtraction, Multiplication and Division

#### 1. Binaryaddition

| Case | Α | ÷ | В | Sum | Carry |

|------|---|---|---|-----|-------|

| 1    | 0 | + | 0 | 0   | 0     |

| 2    | 0 | + | 1 | 1   | 0     |

| 3    | 1 | + | 0 | 1   | 0     |

| 4    | 1 | + | 1 | 0   | 1     |

Infourthcase, abinary additioniscreating as umof (1+1=10) i.e. 0 is written in the given column and a carry of 1 over to the next column.

#### **Example-Addition**

| 0011010 + 001100 = 00100110 | 11       | carry  |

|-----------------------------|----------|--------|

|                             | 0011010  | = 2610 |

|                             | +0001100 | = 1210 |

|                             | 0100110  | = 3810 |

#### 2. BinarySubtraction

**Subtraction and Borrow**, these two words will be used very frequently for the binary subtraction. There are four rules of binary subtraction.

| Case | Α | 15  | В | Subtract | Borrow |

|------|---|-----|---|----------|--------|

| 1    | 0 |     | 0 | 0        | 0      |

| 2    | 1 | -   | 0 | 1        | 0      |

| 3    | 1 | 823 | 1 | 0        | 0      |

| 4    | 0 |     | 1 | 0        | 1      |

Example-Subtraction

| 0011010 - 001100 = 00001110 | 1 1      | borrow |

|-----------------------------|----------|--------|

|                             | 0011010  | = 2610 |

|                             | -0001100 | = 1210 |

|                             | 0001110  | = 1410 |

#### 3. Binary Multiplication

Binary multiplication is similar to decimal multiplication. It is simpler than decimal multiplication because only 0s and 1s are involved. There are four rules of binary multiplication.

| Case | Α | x | В | Multiplication |

|------|---|---|---|----------------|

| 1    | 0 | x | 0 | 0              |

| 2    | 0 | х | 1 | 0              |

| 3    | 1 | x | 0 | 0              |

| 4    | 1 | x | 1 | 1              |

-

#### Example-Multiplication

Example: 0011010 x 001100 = 100111000

| 0011010    | = 2610  |

|------------|---------|

| x0001100   | = 1210  |

| 0000000    |         |

| 0000000    |         |

| 0011010    |         |

| 0011010    |         |

| 0100111000 | = 31210 |

.1'scomplementand2'scomplementnumbersforabinary number

a.1's complement

### 1'scomplement

**1's complement** of a binary number is another binary number obtained by toggling all bits in it, i.e., transforming the 0 bit to 1 and the 1 bit to 0.

Originalvalue 1's complement  $0 \longrightarrow 1$

$\begin{array}{ccc} 0 & & & 1 \\ 1 & \longrightarrow & 0 \end{array}$

Examples:

1'scomplementof7(0111)is8(1000)

1'scomplementof12(1100)is3(0011)

## **Useof1's complement**

The main use of 1's complement is to represent a signed binary number. Apart from this, it is also used to perform various arithmetic operations such as addition and subtraction.

In signed binary number representation, we can represent both positive and negative numbers

## 2'scomplement

2'scomplement of a binary number is 1 added to the 1's complement of the binary number.

| i.e. | Original value   | 1's complement    |             |

|------|------------------|-------------------|-------------|

|      |                  | 2'scomplement1011 | 0100        |

|      |                  | 0100+1=0101       |             |

|      | 1101             | 0010              | 0010+1=0011 |

| lleo | of2's complement |                   |             |

## Useof2's complement

Negative binary numbers are represented in 2's complement form so that the same logic circuit can be used to perform addition as well as subtraction

Subtractionofbinarynumbersin 2'scomplementmethod.

#### Theoperationiscarriedoutbymeansofthefollowingsteps:

(i) Findthe 2'scomplementofthesubtrahend(negativeno.only,because2's complement of positive no. is remain same) of given no..

(ii) Thenitisaddedtotheminuend.(add2'scomplementedwithpositivegivenno.)

(iii) If the final carry overof the sum is 1, it is dropped and the result is positive.

(iv) If there is no carry over, thetwo's complement of the sum will be the result and it is negative.

### Examples:

#### (i) **110110-10110**

#### Solution:

Now,2'scomplementof010110is(101101+1)i.e.101010.Addingthiswith the minuend.

110110 Minuend

#### <u>101010</u> 2'scomplementofsubtrahend

Carryover1 100000 Resultofaddition Afterdroppingthecarryoverwegettheresultofsubtractiontobe100000.

#### (ii) 10110-11010

#### Solution:

2'scomplementof11010is(00101+1)i.e.00110.Hence Minued - 10110

2'scomplementofsubtrahend- <u>00110</u> Resultofaddition- 11100

Asthereisnocarryover, the result of subtraction is negative and is obtained by writing the 2's complement of 11100 i.e. (00011 + 1) or 00100.

Hencethedifferenceis-100.

Use of weighted and Un-weighted codes & write Binary equivalent number for a number in 8421, Excess-3 and Gray Code and vice-versa.

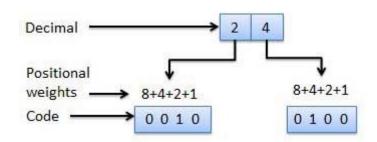

#### Weighted code

Weighted binary codes are those binary codes which obey the positional weight principle.Eachpositionofthenumber representsaspecificweight. Severalsystems of the codes are used to express the decimal digits 0 through 9. In these codes each decimal digit is represented by a group of four bits.

- a. BCD(8421)

- b. 6311

- c. 2421

- d. 642-3

- **e.** 84-2-1

## **UseofWeightedcodes**

- a) Datamanipulationduringarithmeticoperation.

- b) Weightedbinarycodeisessentialfordisplayingnumericvaluesindigital devices such as voltmeters and calculators

- .c)Torepresentthedecimaldigitsincalculators,voltmetersetc.

# Non-WeightedCodes

In this type of binary codes, the positional weights are not assigned. The examples of non-weighted codes are Excess-3 code and Gray code.

## Nonweightedcodes areusedin:

- a) Toperformcertainarithmeticoperations.

- b) Shiftpositionencodes.

- c) Usedforerrordetectingpurpose.

## **Excess-3code**

The Excess-3 code is also called as XS-3 code. It is non-weighted code used to express decimalnumbers.The Excess-3codewordsarederivedfromthe8421BCDcodewords adding (0011)2 or (3)10 to each code word in 8421. The excess-3 codes are obtained as follows –

Example

| Decimal | BC  | D   | Exces | s-3  |

|---------|-----|-----|-------|------|

|         | 84  | 2 1 | BCD + | 0011 |

| 0       | 0 0 | 0 0 | 0 0   | 1 1  |

| 1       | 0 0 | 0 1 | 0 1   | 0 0  |

| 2<br>3  | 0 0 | 1 0 | 0 1   | 0 1  |

| 3       | 0 0 | 1 1 | 0 1   | 1 0  |

| 4       | 0 1 | 0 0 | 0 1   | 1 1  |

| 5       | 0 1 | 0 1 | 1 0   | 0 0  |

| 6       | 0 1 | 1 0 | 1 0   | 0 1  |

| 7       | 0 1 | 1 1 | 1 0   | 1 0  |

| 8       | 1 0 | 0 0 | 1 0   | 1 1  |

| 9       | 1 0 | 0 1 | 1 1   | 0 0  |

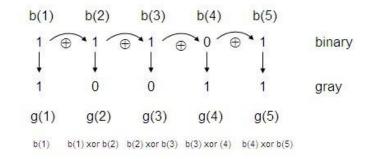

# GrayCode

It is the non-weighted code and it is not arithmetic codes. That means there are no specificweightsassignedtothebitposition. It has a very special feature that, only one

bit will change each time the decimal number is incremented as shown in fig. As only one bit changes at a time, the gray code is called as a unit distance code. The gray code is a cyclic code. Gray code cannot be used for arithmetic operation.

## ConvertabinarynumbertoaGraynumber

Let'sunderstandthealgorithmtogofrombinarytoGray.Seetheconversionfrom'11101' binary to its equivalent in Gray code.

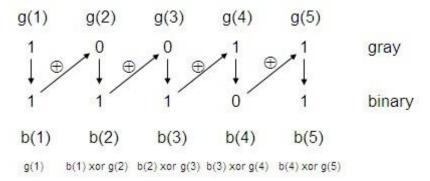

# ConvertaGraynumber toabinarynumber

Let'sunderstandthealgorithmtogofrombinarytoGray.Seetheconversionfrom '11101' binary to its equivalent in Gray code.

# ApplicationofGraycode

- Graycodeispopularlyusedintheshaftpositionencoders.

- Ashaftpositionencoderproducesacodewordwhichrepresentstheangular position of the shaft.

### Importanceof parity Bit.

A parity bit is an extra bit included in binary message to make total number of 1's either odd or even. Parity word denotes number of 1's in a binary string. There are two parity system-even and odd.

# Evenparitysystem

In even parity system 1 is appended to binary string it thereisanodd number of 1's in string otherwise 0 is appended to make tot levennumber of 1's.

# Oddparitysystem

Inoddparitysystem,1isappendedtobinarystringifthereisevenanumber of 1's to make an odd number of 1's

# ImportanceofparityBit.

Thepurposeofaparitybitistoprovideasimplewaytochec Errors k for

# Logic Gates: AND, OR, NOT, NAND, NOR and with truth table.

**EX-ORgates**

# WhatisLogicGates?

Logicgatesaretebalicbuildingblocksofanydigitalsystem.Itisan electroniccircuithavingoneormorethanoneinputandolyoneoutput. Therelationship Letweentheinputandtheoutputisbas dona certain logic. Based on this, logic gates are named as AND gate, OR gate, NOT gate etc.

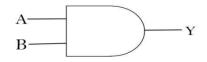

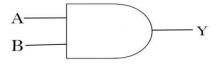

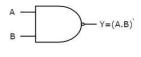

# ANDGate

An AND gate is a logic gate having two or more inputs and  $\epsilon$  singleoutput. An AND gate operates on logical multiplication rules

Expression for AND gate Y=A.B Truth Table of AND gate

| Inj | Input |   |

|-----|-------|---|

| Α   | В     | Y |

| 0   | 0     | 0 |

| 0   | 1     | 0 |

| 1   | 0     | 0 |

| 1   | 1     | 1 |

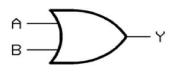

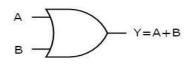

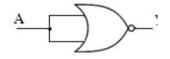

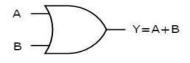

## ORGate

ExpressionforORgateY=A+B

# TruthTable

| Input |   | Output |

|-------|---|--------|

| Α     | В | Y      |

| 0     | 0 | 0      |

| 0     | 1 | 1      |

| 1     | 0 | 1      |

| 1     | 1 | 1      |

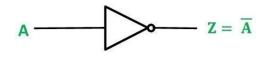

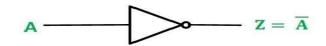

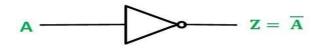

### NOTGate

TheNOTgateisthemostbasiclogicgateofallotherlogicgates.NOTgateisalso known as an **inverter**

NOT gate only has one input and one output it converts 0 into 1 or 1 into 0.

ExpressionforNOTgateZ=2

# TruthTable

| Inputs | Outputs |  |

|--------|---------|--|

| A      | Y       |  |

| 0      | 1       |  |

| 1      | 0       |  |

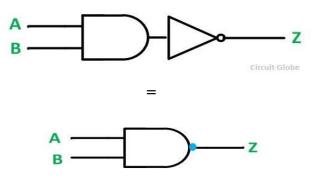

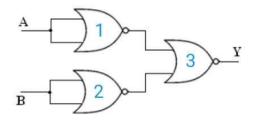

# NANDGate

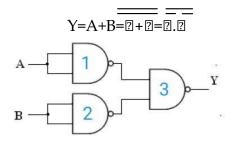

TheNANDgateisaspecialtypeoflogicgateinthedigitallogiccircuit. The NAND gate is the combination of AND -NOT gate

TheNANDgate istheuniversalgate.ItmeansallthebasicgatessuchasAND,OR,and NOT gate can be constructed using a NAND gate. The output state of the NAND gate will be low only when all the inputs are high. Simply, this gate returns the complement result of the AND gate.

ExpressionforNANDgateZ=2.2

# TruthTable

| Input |   | Out Put |

|-------|---|---------|

| А     | В | Z=?.?   |

| 0     | 0 | 0       |

| 0     | 1 | 1       |

| 1     | 0 | 1       |

| 1     | 1 | 0       |

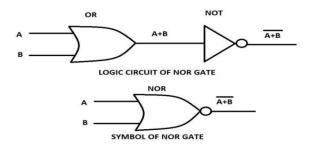

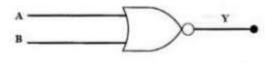

# NORGate

TheNORgateisalsoauniversalgate

TheNORgateisthecombinationoftheOR-NOTgate

TheNORgateistheuniversalgate.ItmeansallthebasicgatessuchasAND,OR, and

NOT gate can be constructed using a NOR gate.

TheoutputstateoftheNORgatewillbehighonlywhenalloftheinputsare low. Simply, this gate returns the complement result of the OR gate

#### ExpressionforNorgateZ=2+2

# TruthTable

| In | put | Out Put |

|----|-----|---------|

| А  | В   | Z=?+?   |

| 0  | 0   | 1       |

| 0  | 1   | 0       |

| 1  | 0   | 0       |

| 1  | 1   | 0       |

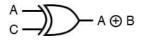

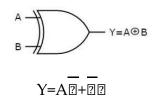

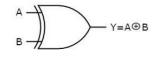

EX-OR

ExpressionforEX-ORgateZ=(2B+A2)

## TruthTable

| Input |   | Out Put |

|-------|---|---------|

| А     | В | Z=A⊕B   |

| 0     | 0 | 1       |

| 0     | 1 | 0       |

| 1     | 0 | 0       |

| 1     | 1 | 0       |

RealizeAND,OR,NOToperationsusingNAND,NORgates.

NANDandNOR gatesprovidethefollowingmeritsinthedigitallogic system design

- 1. Fabrication of NAND and NOR gates are easier than basic gates using in the integrated digital logic families

- 2. NumberoftransistorsusedtodesignNANDandNORgatesarealso less thanANDand ORgates.Sincethecoreareareducesintheintegrated digital circuits.

- 3. The conversion of NAND and NOR are more conveniet indigital design.

- 4. AllotherlogicgatescanberealizedcompletelyusingNANDorNOR gates.

- 5. Anydigitalckt.canbeimplementedperfectlyusingeitherNANDor NOR gates thus these are called as universal gate

### ImplementationofLogicgatesusingNANDGate

#### i) NOTgate

ThelogicsymbolandBooleanexpressionofNOTgateisrepresentedby

NANDequivalentrepresentationforNOTgateis

Theaboveexpression indicates that if the input terminals of NAND gate are Same shown in fig

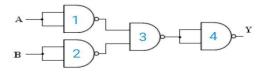

#### ii) ANDGate

ThelogicsymbolandBooleanexpression of AND gate is represented by

Y=A.B

NANDequivalentrepresentationforANDgateis

#### Nowaboveexpressioncandrawnas

\_

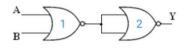

#### iii) **OR gate:**

NANDequivalentrepresentationforORgateis

iv) **NORgate:**

Y=?+? NANDequivalentrepresentationforNORgateis Y=? +?=?+?

=?.?

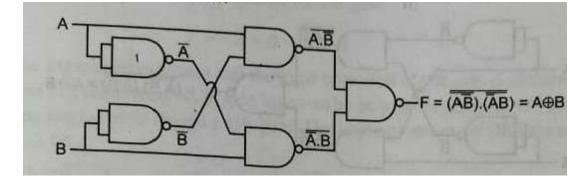

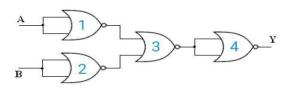

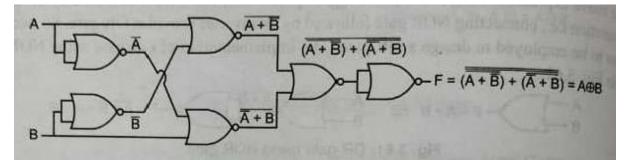

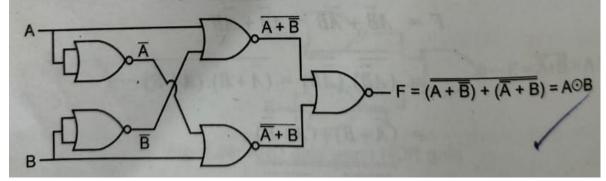

# v) Ex-OR gate:

NANDequivalentrepresentationforEx-ORgateis

Nowaboveexpressioncandrawnas

vi) Ex-NORgate:

$Y=A \odot B= 22+AB$

NANDequivalentrepresentationforEx-NORgateis

## ImplementationofLogicgatesusingNOR Gate

#### i) NOTgate

The logic symbol and Boolean expression of NOT gate is represented by

NORequivalentrepresentationforNOTgateis

$$\frac{Z=?}{=?+?}$$

Nowaboveexpressioncandrawnas

#### ii) AND Gate

ThelogicsymbolandBooleanexpressionofANDgateisrepresented by

Y=A.B NANDequivalentrepresentationforANDgateis Y=A.B=2.2=2.+2

#### iii) ORgate:

The logic symbol and Boolean expression of OR gate is represented by

NORequivalentrepresentationforORgateis

Nowaboveexpressioncandrawnas

## iv) NANDgate:

The logic symbol and Boolean expression of NAND gate is represented by

NORequivalentrepresentationforNANDgateis

# v) Ex-ORgate:

ThelogicsymbolandBooleanexpressionofEx-OR gate is represented by

Y=A?+??NOR

equivalentrepresentationforEx-ORgateis

$$Y = \overline{A2 + 22}$$

$$= (A2).(22)$$

$$= (2+2).(A+2)$$

$$= (2+2)+(A+2)$$

$$= (2+2)+(A+2)$$

Nowaboveexpressioncandrawnas

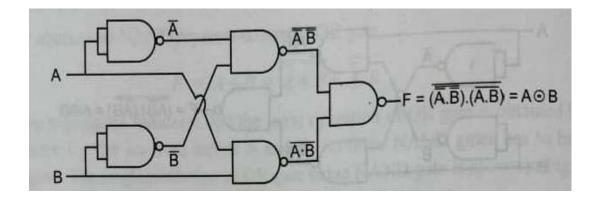

### i) Ex-NORgate:

ThelogicsymbolandBooleanexpression of **Ex-NOR** gate is represented by

$Y=A \odot B= 22 + AB$ NORequivalentrepresentationfor**Ex-NOR** gate is

$$Y = A \odot B = 27 + 27$$

$$= 27 + 27$$

$$= 27 + 27$$

$$= (27).(27)$$

$$=(\overline{2+2}).(\overline{2+2})$$

$$=(\overline{2+2}).(\overline{2+2})$$

$$=(\overline{2+2}).(\overline{2+2})$$

$$=(\overline{2+2})+(\overline{2+2})$$

Nowaboveexpressioncandrawnas

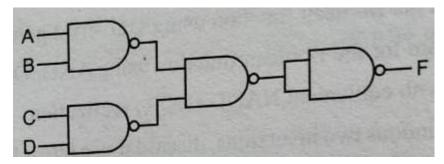

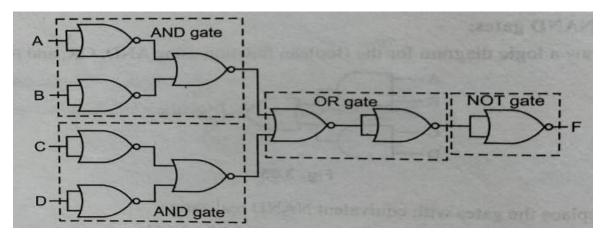

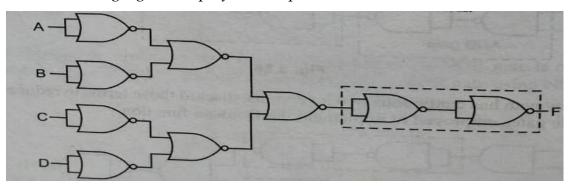

PROCEDURETOIMPLEMENTTHEBOOLEANFUNCTIONUSINGUNIVERSALGATE:

- 1. DrawalogicdiagramfortheBooleanfunctionusingbasicgatesi.e.AND,OR,and NOT

- 2. ReplacethegatewithequivalentNANDorNORrealization.

- 3. If any pathhas continuous two inversions, discard those terms to reduce the number of logic gates employed to implement the Boolean function.

- 4. RedrawthesimplifiedlogicdiagramastheUniversalgatesimplementation of Boolean function.

*Example:ImplementthefollowingBooleanfunctionusingminimumnumberof(i)NAND gates, (ii)NOR gates*

Solution:

GivenBooleanfunction,

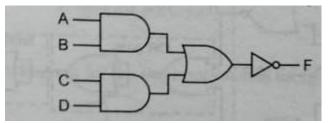

- (i) UsingNANDgates:

- 1. Step:1DrawalogicdiagramfortheBooleanfunctionusingbasicgatesi.e. AND,OR,and NOT

2. Step:2ReplacethegatewithequivalentNANDrealization.

**3**. Step:3Ifanypathhascontinuoustwo inversions,discardthosetermstoreduce the number of logic gates employed to implement the Boolean function.

In this case, both path are having two inversions in series so discard those inverter

4. Step:4RedrawthesimplifiedlogicdiagramastheUniversalgates implementation of Boolean function

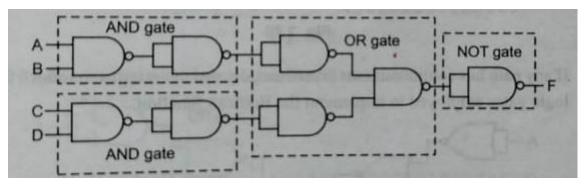

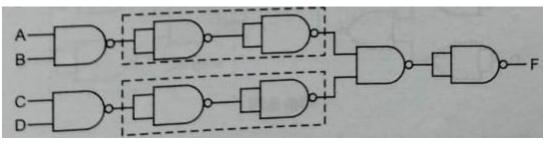

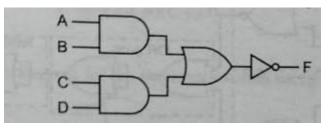

- (ii) UsingNORgates:

- 1. Step:1DrawalogicdiagramfortheBooleanfunctionusingbasicgatesi.e. AND,OR,and NOT

2. Step:2ReplacethegatewithequivalentNORrealization.

3. Step:3Ifanypathhascontinuoustwo inversions, discard those terms to reduce the number of logic gates employed to implement the Boolean function.

Inthiscase, output section ehaving two inversions inseries so discard those inverter

4. Step:4RedrawthesimplifiedlogicdiagramastheUniversalgates implementation of Boolean function

# DifferentpostulatesandDe-Morgan'stheoremsinBoolean algebra.

a. ??=?+?

## Use Of Boolean Algebra For Simplification Of Logic Expression

# WhatisBoolean Algebra?

Boolean Algebra is used to analyze and simplify the digital (logic) circuits. It uses only the binary numbers i.e. 0 and 1. It is also called as **Binary Algebra**or**logical Algebra**. Boolean algebra was invented by **George Boole** in 1854

# RuleinBoolean Algebra

Following are the important rules used in Boolean algebra.

- I. Variable used can have only two values. Binary 1 for HIGH and Binary 0 for LOW.

- II. Complement of a variable is represented by an overbar (-). Thus, complement of variable B is represented as  $\overline{B}$ . Thus if B = 0 then  $\overline{B}$  = 1 and B = 1 then  $\overline{B}$  = 0.

- III. ORingofthevariablesisrepresentedbyaplus(+)signbetweenthem.For example ORing of A, B, C is represented as A + B + C.

- IV. LogicalANDingofthetwoormorevariableisrepresentedbywritingadot between them such as A.B.C. Sometime the dot may be omitted like ABC.

## BASICLAWSOFBOOLEANALGEBRA:

### 1. NOTLaw:

i.

$$0=1$$

ii.  $1=0$

- iii. A=2

- 2. ANDLaws

- iii. A.A= A

- iv. A. 2=0

- 3. ORLaws:

- i. A+0=A

- ii. A+1=1

- iii. A+A= A

- iv. A+ 🗉=1

### 4. CommutativeLaws:

- i. A+A=B+A

- ii. A.B=B.A

- iii. A+B+C=C+B+C

iv. A.B.C=B.C.A=C.A.B

- 5. Associativelaws:

- i. A+(B+C)=(A+B)+C

- ii. A.(B.C)=(A.B).C

- 6. Distributivelaw:

- i. A+BC=(A+B)(A+C)

- ii. A(B+C)=AB+AC

#### BOOLEANTHEOREM

1. A+AB =A

Proof:A+AB=A(B+

$$\mathbb{Z}$$

)+AB

=AB+A $\mathbb{Z}$ +AB

=AB+ $\mathbb{Z}\mathbb{Z}$

=A(B+ $\mathbb{Z}$ )

=A .1

=A

**2. A(A+B)=A** Proof: A(A+B)=A.A+A.B

=A+AB

=A

3. A+2B=A+B

Proof:  $A + \boxed{2}B = A + AB + \boxed{2}B$ =  $A + (A + \boxed{2})B$ = A + B

4. A. (□+B)= A Proof: A.(□+B)=A. □+AB =0+AB

5. AB+A.2=A

6. (A+ B).(A+2)=A

7. (A+ B).( A+C )= A+ BC

8. AC+ 2BC=AC+BC

#### **DEMORGAN'S THEOREM:**

#### DUALITYTHEOREM:

Dualitytheoremsaythatinthelogicfunctionapplyingthefollowingchangesin the AND, OR and NOT operation doesn't affect the output.

- 1. Swap'0'and'1'presentintheexpression.

- 2. ReplacingANDoperationbyORoperation

- 3. ReplacingORoperationbyANDoperation

Examples:

b.

$$A(B+C)=AB+AC$$

Afterapplyingdualitytheoremintheaboveexpression,itbecomes A + (

$$BC) = (A + B) . (A + C)$$

#### **ABSORPTIVETHEOREM:**

**TRANSPOSITION THEOREM:**

USING THE THEOREM & LAWS, SIMPLIFY THE FOLLOWING EXPRESSION

2. **(**A+B)(A+C)

| =A.A+A.C+A.B+B.C | -Distributivelaw         |

|------------------|--------------------------|

| =A+A.C +A.B+B.C  | -IdempotentANDlaw(A.A=A) |

| =A(1+C)+A.B+B.C  | -Distributivelaw         |

| =A+AB+BC         | -IdentityORlaw(1+C=1)    |

| =A(1+B)+BC       |                          |

| =A.1+BC          |                          |

=A+BC

3. 2222+2222+2222+2222+222+22==2222+2222+2222+222+22==2(222+222+222+222+22+2)=2(222+222+222+222+2)=(2+2)(2+2)=A+D4. 222+222+222+222=222+222+222+222=222+222+222+222=222+222+22+22=222+2(2+2)=222+2(2+2)(2+2)=222+2(2+2)(2+2)=222+2(2+2)+22=2(22+2)+2(2+2)=2(22+2)+2(2+2)

```

=?(?+?)+??

```

=??+??+??

# Karnaugh MapFor2,3,4 Variable,SimplificationOfSOP And POS Logic Expression Using K-Map.

### A.BOOLEAN FUNCTION:

Boolean function consists of a set of Boolean variables to represent a number using Boolean connectivity's logical NOT, logical AND, logical OR operations, parenthesis and equality sign. It also known as Boolean expression.

Based on the arrangement of literals and terms Boolean expression is classified in two types such as,

- 1. SumofProduct(SOP)form

- 2. ProductofSum(POS)form

## 1. SumofProduct(SOP)form:

Sum of Product term is consisting of sum (OR operation) of many terms; the terms may consists of single literal or product of many literals (Variables). The sum of the terms is called SOP function.

Example:

- i. F(A,B,C)=222+22+22+222

- ii. F(x,y,z)=??+??+???

- iii. F(A,B,C,D)=2222+2222+2222+2222+2222

## a.StandardSumofProduct(SOP)form:

The SOP form of expression is said to be Standard Sum of Product formor Canonical form expression if the terms present in the expression contains all the literals present in the function.

Each individual term present in the expression must have all the literalsof a function.

ThestepstoconvertnoncanonicalSOPtoCanonicalorstandard SOP.

- 1. Findthemissingliteralineachproductterm.

- 2. Multiply(AND)eachproducttermtothetermhavingmissingliteralbyORingthe missing literal and its complement.

- 3. Expandthetermsandrearrangetheliteralsintheproduct terms.

- 4. Reduce the expression by omitting the repeated terms if any (i.e. A+A=A)

Example:

**i)** ConvertthegivenexpressionF(A,B,C)= A+ℤCintocanonicalSOP form.

Inthe given expression, literal Band C are missing in the 1<sup>st</sup> product term. So (B+ $\mathbb{Z}$ ) and (C+ $\mathbb{Z}$ ) are multiplied (AND) with the term A. Similarly, literal A is missing in the 2<sup>nd</sup> product term. So (A+ $\mathbb{Z}$ ) is multiplied (AND) with the product term  $\mathbb{Z}$ C.

Given;

$$F(A,B,C)=2+2\overline{2}$$

$$=2(2+2)+2\overline{2}(2+2)$$

$$=22+2\overline{2}+2\overline{2}\overline{2}+2\overline{2}\overline{2}$$

$$=22(2+2)+2\overline{2}(\overline{2}+2)+2\overline{2}\overline{2}+\overline{2}\overline{2}\overline{2}$$

$$=222+2\overline{2}\overline{2}+2\overline{2}\overline{2}+2\overline{2}\overline{2}+2\overline{2}\overline{2}$$

# 2. ProductofSum(POS)form:

Product of Sum (POS) term is consisting of sum (AND operation) of many terms;the terms may consists of single literal or product of many literals (Variables).The product of the set of sum terms is called POS function.

Example:

- i. F(A,B,C)=(2+2+2)(2+2)(2+2)(2+2)(2+2)

- ii. F(x,y,z)=(2+2)(2+2)(2+2+2)

- iii. F(A,B,C,D) = (2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2)(2+2+2)(2+2+2)(2+2+2)(2+2)(2+2+2)(2+2+2)(2+2+2)(2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2+2)(2+2)(2+2+2)(2+2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2)(2+2

# a)StandardProductofsum(POS)form:

The POS form of expression is said to be **Product of sum** form or Canonical form expression if the terms present in the expression contains all the literalspresent in the function.

Each individual term present in the expression must have all the literals of a function.

ThestepstoconvertnoncanonicalPOStoCanonicalorstandard POS.

- 1. Findthemissingliteralineachsumterm.

- 2. OReachsumtermtothetermhavingmissingliteralbyANDing(product)the missing literal and its complement.

- 3. Expandthetermsandrearrangetheliteralsinthesumterms.

- 4. Reduce the expression by omitting the repeated terms if any (i.e. A. A=A) Let us

see an example here.

## ConvertthegivenexpressionF(A,B,C)=(A+B)(B+C)intocanonicalPOSform.

In the given expression, literal C is missing in the 1<sup>st</sup>sum term. So  $(C.\overline{C})$  is added with the term (A+B).Similarly,literalAismissinginthe2<sup>nd</sup>sumterm.So(A.A)isadded with the term (B+C).

Given;

$$F(A,B,C)=(?+?)(?+?)$$

=(?+?)+(?.?)(?+?)+(?.?)

=(2+2+2)(2+2+2)(2+2+2)(2+2+2)

#### 3. SIMPLIFICATIONOFBOOLEANFUNCTION:

There are 3-different basic simplification methods available for minimizing Boolean function

- 1. Booleanalgebra

- 2. Karnaughmap

- 3. QuineMcCluskeymethod

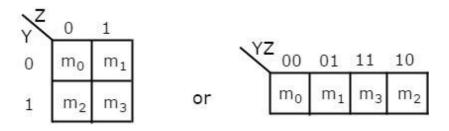

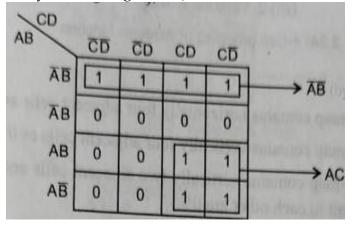

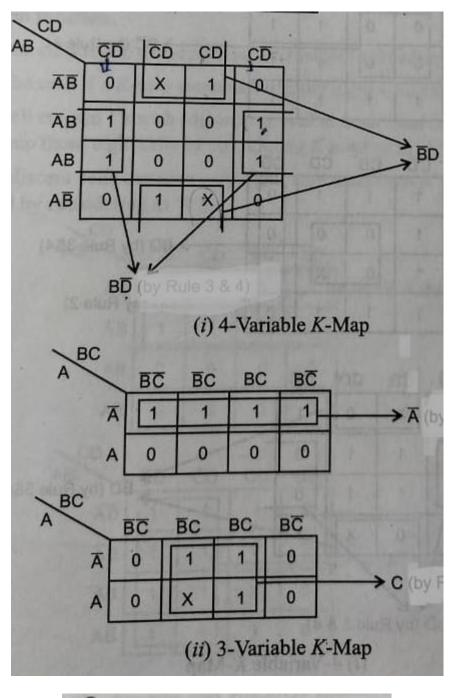

#### a. KARNAUGHMAP(K-MAP):

Simplifying theBoolean functions using Boolean postulates and theorems. It is time consuming process and to re-write the simplified expressions after each step.

To overcome this difficulty,**Karnaugh**introduced a method for simplification of Boolean functions in an easy way.

This method is a graphical method for simplification of Boolean function which consists of 2<sup>n</sup> cells for 'n' variables. Each cell of K-map represents one of the **minterm**. The adjacent cells are differed only in single bit position.

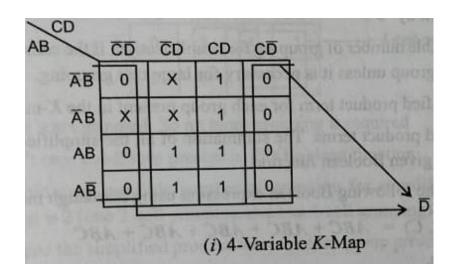

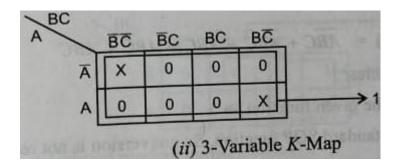

#### ClassificationofK-Map:

DependsonthenumberofvariablesusedintheK-mapitisclassified as

- ii. 3-Variablek-map

- iii. 4-Variablek-map

- iv. 5-Variablek-map

#### 1. 2-Variablek-map:

Thenumberofvariable(n)=2 The

number of cells  $=2^n=2^2=4$

• The possible combinations of grouping 2 adjacent minterms are {( $m_0, m_1$ ), ( $m_2, m_3$ ), ( $m_0, m_2$ ) and ( $m_1, m_3$ )}.

| Vari | able | Minterm        | S              |

|------|------|----------------|----------------|

| А    | В    | Representation | mi             |

| 0    | 0    | [?] [?]        | $m_1$          |

| 0    | 1    | ??             | m <sub>2</sub> |

| 1    | 0    | ? ?            | m <sub>3</sub> |

| 1    | 1    | ? ?            | m4             |

(Mintermsof2-variableexpression)

#### 2. 3-Variablek-map:

Thenumberofvariable(n)=3 The

number of cells  $=2^n=2^3=8$

| X | 00             | 01             | 11             | 10             |

|---|----------------|----------------|----------------|----------------|

| 0 | m <sub>0</sub> | m <sub>1</sub> | m <sub>3</sub> | m <sub>2</sub> |

| 1 | m <sub>4</sub> | m <sub>5</sub> | m <sub>7</sub> | m <sub>6</sub> |

## 3. 4-Variablek-map:

Thenumberofvariable(n)=4

Thenumberofcells=2<sup>n</sup>=2<sup>4</sup>=16

| wx YZ | 00              | 01              | 11              | 10              |

|-------|-----------------|-----------------|-----------------|-----------------|

| 00    | m <sub>0</sub>  | m <sub>1</sub>  | m <sub>3</sub>  | m <sub>2</sub>  |

| 01    | m <sub>4</sub>  | m <sub>5</sub>  | m <sub>7</sub>  | m <sub>6</sub>  |

| 11    | m <sub>12</sub> | m <sub>13</sub> | m <sub>15</sub> | m <sub>14</sub> |

| 10    | m <sub>8</sub>  | m <sub>9</sub>  | m <sub>11</sub> | m <sub>10</sub> |

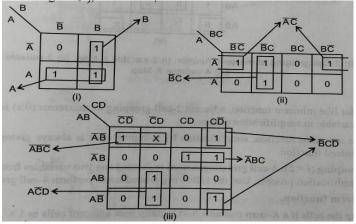

# Don'tcarecondition:

In some digital systems, nonessential minterms or maxterms may be introduced intheinputsequences.Suchnonessentialmintermsormaxtermsarecalledasdon'tcare condition in the Boolean expression.

These nonessential terms never occur in the input sequence of the system.

Normally, in K-Map don't care conditions are represented by symbol 'X'. Don't care values can be taken as either '0' or '1'.

Don't care conditions occur in the digital system sunder the following condition:

- i. If certain combinations of input variables are never occur, then the output functions of such combinations are considered as nonessential or don't care condition.

- ii. If certain combinations of variables are irrelevant even all the input combination of variables occurs, then the output functions of such combinations are considered as nonessential or don't care condition.

# GroupingcellforMinimization:

InK-map,mintermsaremarkedby'1'

maxterm are marked by'0'

don'tcarearemarkedby'd'or'x'i.eX='0'or '1'

In minterm function, don't care condition is considered as '1' if necessary for simplification or grouping cell. Else, it is marked by '0'

In maxterm function, don't care condition is considered as '0' if necessary for simplification or grouping cell. Else, it is marked by '1'

Grouping of cell or Loop of cell is process of combining adjacent cells for simplification.

Groupingisobtainedbycombining1'sor0'sof2<sup>i</sup>numbercells,wherei=0,1,2...,n (n -->number of variables used in the Boolean function.)

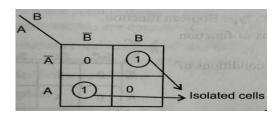

# IsolationCellor Singlecellgroup(i=0):

- i. K-mapcelliscalledasIsolationgroupwhennoadjacenthorizontalorvertical cell is '1'for minterm and'0' for maxterm.

- ii. Isolationcellcan'tbeusedforsimplification,itgivestheBooleanfunctionremain as same

**2-Cellgroup(i=1):**2cellgroupingisusedtodiscardanyvariablefromtwoadjacent cell in the simplification process

### **ProcedureforMintermfunction:**

- i. Groupthecellifak-mapcontainshorizontallyadjacentpair(2cell)ofcellsas1's

- ii. Groupthecellifak-mapcontainsverticallyadjacentpair(2cell)ofcellsas1's

- iii. If any cell contain 1 with a djacent vertical or horizontal cell as don't care condition 'X' then group those two cells by considering X=1

- iv. If any cell contain only don't care condition' X' then don't group those cells (Discard by considering as X=0)

#### ProcedureforMaxtermfunction:

- i. Groupthecellifak-mapcontainshorizontallyadjacentpairofcellsas0's

- ii. Groupthecellifak-mapcontainsverticallyadjacentpair(2cell)ofcellsas0's

- iii. If any cell contain 0 with a djacent vertical or horizontal cell as don't care condition 'X' then group those two cells by considering X=0

- iv. If any cell contain only don't care condition' X' then don't group those cells (Discard by considering as X=1)

| A           | and the | 13 | 0  | 1. 5      | DIAN    | Contraction | i.Um  | arme in a |

|-------------|---------|----|----|-----------|---------|-------------|-------|-----------|

| B B         |         |    |    | ABC       | BC      | BC          | BC    | BČ        |

| A 0 0       |         |    |    | Ā         | 0       | 1           | X     | 0         |

| A 0 1       |         |    |    | A         | 0       | 1           | 1     | 1 1       |

| (i)         |         |    |    | Earned of | at or a | (i          | i)    | . martali |

|             | BCD     | CD | ĒD | CD        | CD      |             |       |           |

|             | AB      | 0  | 1  | 0         | 1       |             |       |           |

|             | ĀB      | 0  | 1  | x         | 1       |             |       |           |

|             | AB      | 1  | 0  | 0         | 1       |             |       |           |

| N O HOME Y  | AB      | 0  | 1  | 15        | x       |             |       |           |

| Jam der har |         |    | (1 | ii)       | X       | 100         | - Mai |           |

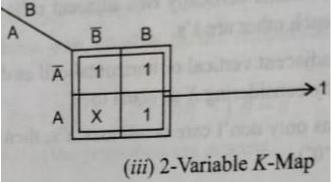

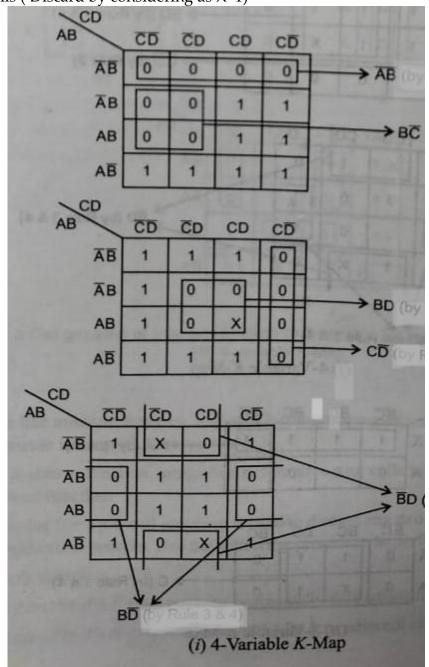

**4-Cellgroup(i=2):**4cellgroupingisusedtodiscardanytwovariablesfromfour(4) adjacent cells in the simplification process

#### ProcedureforMintermfunction:

- i. Groupthecellifak-mapcontainshorizontallyfour(4)adjacentofcellsas1's

- ii. Groupthecellifak-mapcontainsverticallyfour)4)adjacentpailofcellsas1's

- iii. Group the cell If a K-map contain vertically two adjacent cell and horizontal two adjacent cellwhich adjacent to each other are 1's.

- iv. If any cellcontain 1's with adjacent vertically or horizontal cell as don't care condition 'X' then group those four cell by considering X=1.

- v. If any adjacent cell contain only don't care condition 'X' then don't group thosecells ( Discard by considering as X=0)

#### ProcedureforMaxtermfunction:

- i. Groupthecellifak-mapcontainshorizontallyfour(4)adjacentofcellsas0's

- ii. Groupthecellifak-mapcontainsverticallyfour)4)adjacentpailofcellsas0's

- iii. Group the cell If a K-map contain vertically two adjacent cell and horizontal two adjacent cellwhich adjacent to each other are 0's.

- iv. If any cellcontain 1's with adjacent vertically or horizontal cell as don't care condition 'X' then group those four cell by considering X=0.

- v. If any adjacent cell contain only don't care condition 'X' then don't group thosecells ( Discard by considering as X=1)

**8-Cellgroup(i=3):**8cellgroupingisusedtodiscardanythree(3)variablesfrom eight (8) adjacent cells in the simplification process

#### ProcedureforMintermfunction:

- i. Groupthecellifak-mapcontainshorizontallyeight(8)adjacentofcellsas1's

- ii. Groupthecellifak-mapcontainsverticallyeight(8))adjacentpailofcellsas1's

- iii. If any cell contain 1's with adjacent vertically or horizontal cellas don't care condition 'X' then group those eight (8) cell by considering X=1.

- iv. If any adjacent cell contain only don't care condition 'X' then don't group thosecells ( Discard by considering as X=0)

#### **ProcedureforMaxtermfunction:**

- i. Groupthecellifak-mapcontainshorizontallyeight(8)adjacentofcellsas0's

- ii. Groupthecellifak-mapcontainsverticallyeight(8))adjacentpailofcellsas0's

- iii. If any cell contain 0's with adjacent vertically or horizontal cellas don't care condition 'X' then group those eight (8) cell by considering X=0.

- iv. If any adjacent cell contain only don't care condition 'X' then don't group thosecells ( Discard by considering as X=1)

| AB | CD | CD | CD | CD |        |

|----|----|----|----|----|--------|

| ĀB | 1  | 1  | 1  | 1  | 00 D   |

| ĀВ | 1  | 1  | 1  | 1  | 12-1-1 |

| AB | 0  | 0  | 0  | 0  | >/     |

| AB | 0  | 0  | 0  | 0  | 1. 1   |

| AB | CD | ĒD | CD | CD | the Site          |

|----|----|----|----|----|-------------------|

| ĀB | 0  | 0  | 1  | 0  |                   |

| ĀВ | 0  | 0  | 0  | 1  | Appendiate of the |

| AB | 0  | 0  | ×  | 1  | C-UTIN CAL        |

| AB | 0  | 0  | 1  | 1  |                   |

#### SHORTQUESTIONSANDANSWERS

#### 1. Definedigitalsystem?

Ans.A digital system is a system which deals with discrete signal. The input and output of this system is two binary value which is 0 and 1. Examples of digital systems are mobile phones, radio, megaphones and many more

#### 2. Listtheapplicationsofdigitalsystem?

Ans.MobilePhones,CalculatorsandDigitalComputers

Radios and communication Devices.

#### 3. Whatismeantbybit?

Ans. Single digit that used to represent the number is called bit i.e 1 or 0

#### 4. Whatisradixnumbersystem?

Ans. Radix (base)number systemisa generalrepresentationofallthenumber system. It represent the weight of each digits present in the number system. Example:

Base of binary no. system =2 Baseofoctalno.system =8 Baseofhexadecimalno.system=16

#### 5. Definebinarycode?

**Ans.** A group of binary bit that are used to represent the characters, numbers, lettersor words or symbol iscalled asbinary codes.

The digital data is represented, stored and transmitted as group of binary bits. This group is also called asbinary code. The binary code is represented by the number as well as alphanumeric letter.

#### 6. Whatareweightedbinarycodes?

**Ans.** Acodewhichconsistsofbitweightforeachdigitpresentinthebinary code is called weighted binary codes

Example: BCDcodes

#### 7. Whatarenon-weightedbinarycodes?

Ans. Acodewhichisnothavinganybitweightforthedigitpresentinthe binary code is called non-weighted binary codes

Example:Excess-3code,graycode.

#### 8. Whatisgraycode?Whyisitcalledasreflectivecodeandcycliccode?

**Ans.**Itisthe non-weightedbinary code, that means thereare nospecific weights assigned to the bit position. only one bit position will changeeach time the decimal number is incremented so called reflective code. Also the adjacent gray representation differs in only binary bit hence it is referred as cyclic code.

#### 9. StatetheassociativepropertyofBooleanalgebra

**Ans.** Associative law defines that the grouping of variable in the multivariable AND and OR operation does not change the output.

i. A+(B+C)=(A+B)+C

ii. A.(B.C)=(A.B).C

#### 10. StatethedistributivepropertyofBooleanalgebra

**Ans**. Associative law defines that the distribution of variable with AND operation over OR operation is equal to distribution of variable with OR operation over AND operation

i. A+BC=(A+B)(A+C)

ii. A(B+C)=AB+AC

#### 11. StatetheDeMorgan'stheorem

- i. ?.?=?+?

- ii. ?+?=?.?

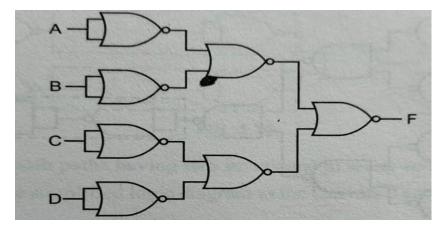

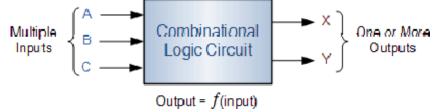

#### 2. COMBINATIONALLOGICCIRCUITS

#### Givetheconceptofcombinationallogic circuits:

Acombinational circuitisthedigitallogic circuitin which the output dependson the combination of present inputs applied to the circuit and It does not depend past input

Combinational circuits are developed using combination of AND, OR, NOT, NAND, and NOR logic gates.

CombinationalLogic Circuitsare memory lessdigitallogiccircuitswhoseoutput at any instant in time depends only on the combination of its inputs

The combinational logic circuits have no feedback circuit is used.

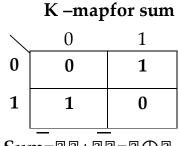

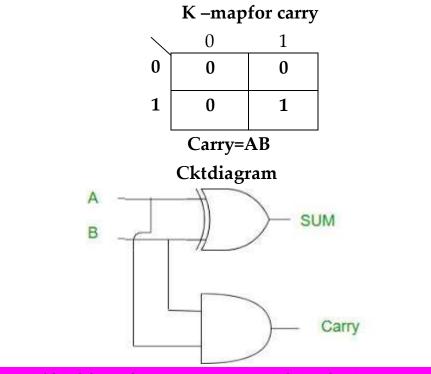

#### Halfaddercircuitandverifyitsfunctionalityusingtruthtable:

Halfadderisacombinationalcircuitwhichconsistsoftwobinaryinputvariables called augend and addendand two binary output variables called sum and carry. In the addition result, the lower significant bit is called as sum and the higher significant bit is called as carry.

Truthtable

| Tuttiable |      |       |     |  |  |  |

|-----------|------|-------|-----|--|--|--|

| Ir        | nput | Outp  | ut  |  |  |  |

| А         | В    | Carry | Sum |  |  |  |

| 0         | 0    | 0     | 0   |  |  |  |

| 0         | 1    | 0     | 1   |  |  |  |

| 1         | 0    | 0     | 1   |  |  |  |

| 1         | 1    | 1     | 0   |  |  |  |

| In | iput | Outpi | ut  |

|----|------|-------|-----|

| А  | В    | Carry | Sum |

| 0  | 0    | 0     | 0   |

| 0  | 1    | 0     | 1   |

| 1  | 0    | 0     | 1   |

| 1  | 1    | 1     | 0   |

|    |      |       |     |

Sum=??+??=?⊕?

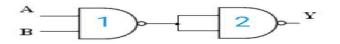

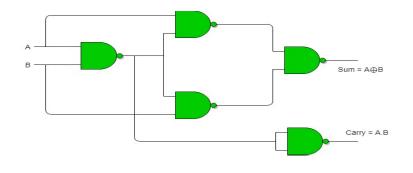

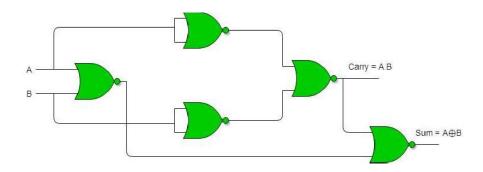

${\bf Realizea Half-adderusing NAND gates only and NOR gates only.}$

Half-adderusingNANDgates

#### Half-adderusingNANDgates

#### Fulladdercircuitandexplainitsoperationwithtruthtable:

Full adder is a combinational circuit which consists of three binary input variables called augend and addendand two binary output variables called sum and carry. In the addition result, the lower significant bit is called as sum and the higher significant bit is called as carry

| IIutiltable |   |     |      |        |  |  |

|-------------|---|-----|------|--------|--|--|

| Inputs      |   |     | Οι   | utputs |  |  |

| А           | В | Cin | Cout | S      |  |  |

| 0           | 0 | 0   | 0    | 0      |  |  |

| 0           | 0 | 1   | 0    | 1      |  |  |

| 0           | 1 | 0   | 0    | 1      |  |  |

| 0           | 1 | 1   | 1    | 0      |  |  |

| 1           | 0 | 0   | 0    | 1      |  |  |

| 1           | 0 | 1   | 1    | 0      |  |  |

| 1           | 1 | 0   | 1    | 0      |  |  |

| 1           | 1 | 1   | 1    | 1      |  |  |

Truthtable

For Sum

| BC | <sup>in</sup> 00 | 01             | _ 11           | 10             |

|----|------------------|----------------|----------------|----------------|

| 0  | 0                | $(\mathbf{i})$ | 0              | $(\mathbf{i})$ |

| 1  | (1)              | 0              | $(\mathbf{i})$ | 0              |

$Sum = \overline{A} \ \overline{B}C_{in} + \overline{A}\overline{B}\overline{C}_{in} + \overline{A}\overline{B} \ \overline{C}_{in} + A\overline{B}C_{in}$

K-mapcanbesimplifiedas

$$SUM = \overline{A} \ \overline{B} C_{in} + \overline{A} \ \overline{B} \ \overline{C}_{in} + \overline{A} \ \overline{B} \ \overline{C}_{in} + \overline{A} \ \overline{B} \ \overline{C}_{in} + \overline{A} \ \overline{B} \ C_{in} \ (\overline{A} \ \overline{B} + \overline{A} \ \overline{B})$$

$$= C_{in} \left[ (\overline{A} + B) \cdot (A + \overline{B}) \right] + \overline{C}_{in} \ (\overline{A} \ \overline{B} + \overline{A} \ \overline{B})$$

$$= C_{in} \ (\overline{A} \ \overline{B} \cdot \overline{\overline{A}} \ \overline{B}) + \overline{C}_{in} \ (\overline{A} \ \overline{B} + \overline{A} \ \overline{B})$$

$$= C_{in} \ (\overline{A} \ \overline{B} + \overline{A} \ \overline{B}) + \overline{C}_{in} \ (\overline{A} \ \overline{B} + \overline{A} \ \overline{B})$$

$$= C_{in} \ (\overline{A} \ \overline{B} + \overline{A} \ \overline{B}) + \overline{C}_{in} \ (\overline{A} \ \overline{B} + \overline{A} \ \overline{B})$$

$$= C_{in} \ (\overline{A} \ \overline{B} + \overline{A} \ \overline{B})$$

$$= C_{in} \ (\overline{A} \ \overline{B} + \overline{A} \ \overline{B})$$

$$= C_{in} \ (\overline{A} \ \overline{B} + \overline{A} \ \overline{B})$$

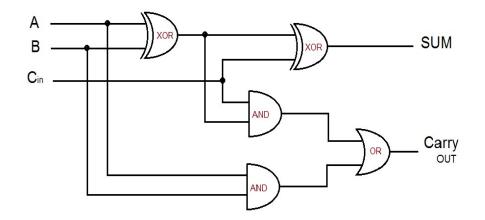

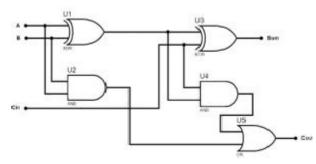

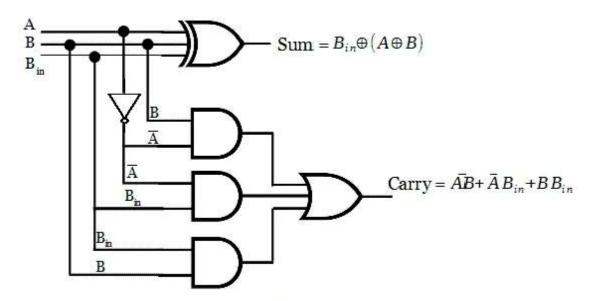

Fulladdercircuitdiagram

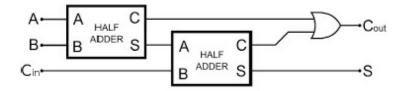

#### Realizefull-adderusingtwoHalf-addersandanOR– gateandwritetruth table.

Thefulladdercanbeimplementedwithtwohalfaddersby cscading them.ThesumoutputoffirsthalfadderisEx-ORofAandB. Thesum outputof full adder is Ex-OR of Cin and output of first half adder.

> Truthtable Outputs Inputs В S А  $C_{\text{in}}$ Cout

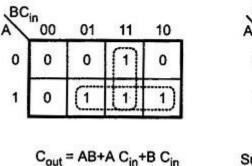

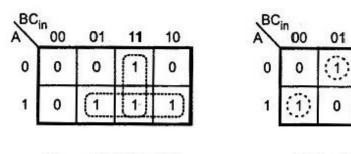

#### k-map

For Carry (Cout)

For Sum

Cout = AB+A Cin+B Cin

Sum = A BCin+ABCin+AB Cin+ABCin

11

0

(i)

10

1

0

K-mapcanbesimplifiedas

$SUM = \overline{A} \overline{B} C_{in} + \overline{A} \overline{B} \overline{C}_{in} + A \overline{B} \overline{C}_{in} + A \overline{B} C_{in}$  $= C_{in} (\overline{A} \overline{B} + A \overline{B}) + \overline{C}_{in} (A \overline{B} + \overline{A} \overline{B})$  $= C_{in} [(\overline{A} + \overline{B}) \cdot (A + \overline{B})] + \overline{C}_{in} (A \overline{B} + \overline{A} \overline{B})$  $= C_{in} (\overline{A} \overline{B} \cdot \overline{\overline{A}} \overline{B}) + \overline{C}_{in} (A \overline{B} + \overline{A} \overline{B})$  $= C_{in} (\overline{A} \overline{B} + \overline{\overline{A}} \overline{B}) + \overline{C}_{in} (A \overline{B} + \overline{A} \overline{B})$  $= C_{in} (\overline{A} \overline{B} + \overline{\overline{A}} \overline{B}) + \overline{C}_{in} (A \overline{B} + \overline{A} \overline{B})$  $= C_{in} (\overline{A} \overline{B} + \overline{\overline{A}} \overline{B}) + \overline{C}_{in} (A \overline{B} + \overline{A} \overline{B})$  $= C_{in} \oplus (A \oplus \overline{B})$

Cout=???;+???;+??

$$=(2+2)22_{22}+(2+2)22_{22}+22$$

=222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{22}+222\_{

Blockdiagram

#### Circuit diagram

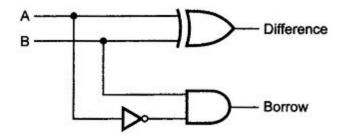

#### Fullsubtractorcircuitandexplainitsoperationwithtruthtable.:

a. Half adder circuit and verify its functionality using truth

**table:**Half subtract is a combinational circuit which consists of two binary input variables calledminuendand

subtrahendandtwobinaryoutputvariablescalleddifferenceand borrow. In the two bit result, the lower significant bit is called as difference and the higher significant bit is called as borrow.

| Α | В | Borrow | Difference |

|---|---|--------|------------|

| 0 | 0 | 0      | 0          |

| 0 | 1 | 1      | 1          |

| 1 | 0 | 0      | 1          |

| 1 | 1 | 0      | 0          |

#### Truthtable

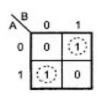

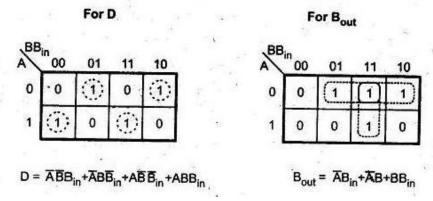

K- map

For Difference

Difference = AB + AB = A⊕B For Borrow

Borrow = AB

Logicdiagram

#### b.Fullsubtractorcircuit ndexplainitsoperationwithtruthtable.:

Fullsubtractionisacombinationalcircuitwhichconsistsofthreebinaryinput variablescalledminuendsandsubtrahends andtwobinaryoutputvariablescalled difference and borrow out. In the subraction result, the lower significant bit is called as differenceand the higher significant bit is called as borrowout

#### Truthtable

| Inputs |   |     | Out | puts |

|--------|---|-----|-----|------|

| A      | в | Bin | D   | Bout |

| 0      | 0 | 0   | D   | 0    |

| 0      | 0 | 1   | 1   | 1    |

| 0      | 1 | 0   | 1   | 1    |

| 0      | 1 | 1   | 0   | 1    |

| 1      | 0 | 0   | 1   | 0    |

| 1      | 0 | 1   | 0   | 0    |

| 1      | 1 | 0   | 0   | 0    |

| 1      | 1 | 1   | 1   | 1    |

Table 3.9 Truth table for full-subtractor

Difference =  $\overline{A} \ \overline{B}B_{in} + \overline{A} B \ \overline{B}_{in} + A \ \overline{B} \ \overline{B}_{in} + A \ B B_{in}$ =  $B_{in}(\overline{A} \ \overline{B} + A B) + \overline{B}_{in}(\overline{A} \ B + A \ \overline{B})$ =  $B_{in}(A \odot B) + \overline{B}_{in}(A \oplus B)$ =  $B_{in}(\overline{A \oplus B}) + \overline{B}_{in}(A \oplus B)$ =  $B_{in}(\overline{A \oplus B}) + \overline{B}_{in}(A \oplus B)$

Logic circuit for Full subtractor

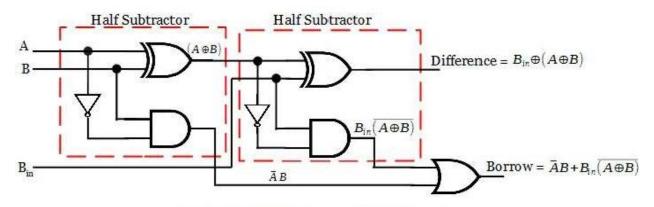

## 2.5Realizefull-subtractionusingtwoHalf-subtractor andanOR–gateand write truth table.

The full subtractor can be implemented with two half subtractors by cascading them. The difference output of first half subtractor is Ex-OR of A and B. The difference output of full subtractor is Ex-OR of Bin and output of first half subtractor.

Similarly, the borrow output of first half subtractor is ORed with the borrow output of second half subtractor toget the borrow output of full subtractor.

Simplification of Difference and Borrow

Difference =

$$\overline{A} \ \overline{B} B_{in} + A B B_{in} + A \overline{B} B_{in} + A B B_{in}$$

=  $B_{in} (\overline{A} \ \overline{B} + A B) + \overline{B}_{in} (\overline{A} B + A \overline{B})$

=  $B_{in} (A \odot B) + \overline{B}_{in} (A \oplus B)$

=  $B_{in} (\overline{A \oplus B}) + \overline{B}_{in} (A \oplus B)$

=  $B_{in} \oplus (A \oplus B)$

Borrow =

$$\overline{A} B + \overline{A} B_{in} + B B_{in}$$

=  $\overline{A} B + \overline{A} B_{in} (B + \overline{B}) + B B_{in} (A + \overline{A})$

=  $\overline{A} B + \overline{A} B B_{in} + \overline{A} \overline{B} B_{in} + A B B_{in} + \overline{A} B B_{in}$

=  $\overline{A} B (1 + B_{in} + B_{in}) + \overline{A} \overline{B} B_{in} + A B B_{in}$

=  $\overline{A} B + \overline{A} \overline{B} B_{in} + A B B_{in}$

=  $\overline{A} B + B_{in} (\overline{A} \overline{B} + A B)$

=  $\overline{A} B + B_{in} (A \odot B)$

=  $\overline{A} B + B_{in} (\overline{A} \oplus B)$

Using the simplified boolean expressions for difference and l orrowoutput, the full subtractor can be realized

Realization of full subtractor with two half subtractors

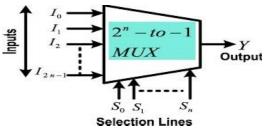

#### 2.7Operationof4X1Multiplexersand1 X4demultiplexer

**Multiplexer** is a cominational circuit that has maximum of 2<sup>n</sup> number data inputs, 'n' number of selection controllines and single output line. Oe of these data inputs will be connected to the output based on the values of selection lines. Shown in figure.

$\label{eq:Where I0,I1,I3,I4,...,In} are the input line, Y is the output line and S_0, S_1, \dots, S nare the selection line.$

#### a.4x1Multiplexer

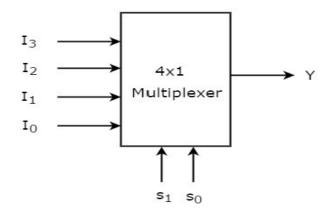

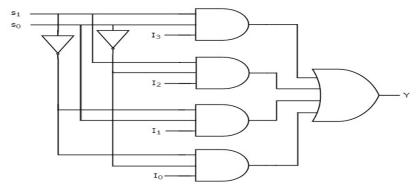

4x1MultiplexerhasfourdatainputsI<sub>3</sub>,I<sub>2</sub>,I<sub>1</sub>&I<sub>0</sub>,twoselectionliness<sub>1</sub>&s<sub>0</sub>andone output Y. The **block diagram** of 4x1 Multiplexer is shown in the following figure.

One of these 4 inputs will be connected to the output based on the combination of inputs present at these two selection lines. Truth table of 4x1 Multiplexer is shown below.

| Selection Lines |    | Output         |

|-----------------|----|----------------|

| S <sub>1</sub>  | So | Y              |

| 0               | 0  | Io             |

| 0               | 1  | l <sub>1</sub> |

| 1               | 0  | I <sub>2</sub> |

| 1               | 1  | 13             |

Logiccircuitdiagram

#### **De-Multiplexer**:

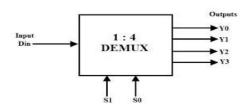

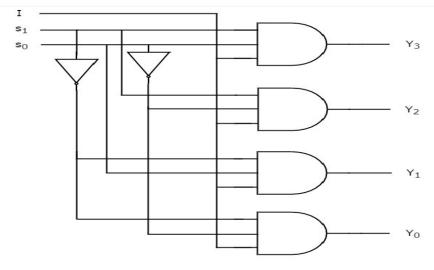

**De-Multiplexer**is a combinational circuit that performs the reverse operation of Multiplexer. It has single input, 'n' selection lines and maximum of 2<sup>n</sup> outputs. De-Multiplexer is also called as **De-Mux**.

#### 1x4De-Multiplexer

1x4 De-Multiplexer has one input I, two selection lines, s1& s0and four outputs Y3, Y2, Y1&Y0. Theblock diagramof 1x4 De-Multiplexer is shown in the following figure.

The single input 'I' will be connected to one of the four outputs, Y3to Y0based on the values of selection lines s1& s0. TheTruth tableof 1x4 De-Multiplexer is shown below.

| Selection<br>inputs |    | outputs |    |       |    |

|---------------------|----|---------|----|-------|----|

| $S_1$               | So | Y3      | Y2 | $Y_1$ | Y0 |

| 0                   | 0  | 0       | 0  | 0     | 1  |

| 0                   | 1  | 0       | 0  | 1     | 0  |

| 1                   | 0  | 0       | 1  | 0     | 0  |

| 1                   | 1  | 1       | 0  | 0     | 0  |

From the above Truth table, we can directly write the **Boolean functions** for each output as

$Y_{0}=I$   $S_{1}S_{0}Y_{1}=IS_{1}$   $S_{0}Y_{2}=IS_{1}$   $S_{0}Y_{3}=I$   $S_{1}S_{0}$ 55

Logiccircuitdiagram

#### WorkingofBinary-DecimalEncoder&3 X8Decoder.

#### a.Decoder

Decoder isacombinational circuit that has multiple input multiple output that is 'n' number of input lines and maximum of 2<sup>n</sup> number of output lines.

OneoftheseoutputswillbeactiveHighbasedonthecombinationofinputs present, when the decoder is enabled. That means decoder detects a particular code. i.e Inthedecoder,thecombinationofinput informationlinesdefinethelog coutputofany one. outputlineaslogichighat atimeandtherestoftheoutputlinesarebeigfixedto logic 0. The outputs of the decoder are nothing but the min termsof 'n' input variableslines, when it is enabled.

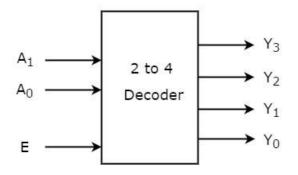

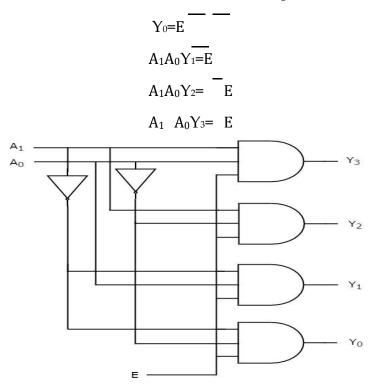

### 2 to4Decoder

Let2to4DecoderhastwoinputsA<sub>1</sub>&A<sub>0</sub>andfouroutputsY<sub>3</sub>,Y<sub>2</sub>,Y<sub>1</sub>&Y<sub>0</sub>. The **block diagram** of 2 to 4 decoder is shown in the following figure.

```

i.e inputlines'n'=2

```

output lines=2<sup>n</sup>=2<sup>2</sup>=4

One of these four outputs will be '1' for each combination of inputs when enable, Eis'1'. The **Truth table** of 2 to 4 decoder is shown below.

| Enable | Inp            | outs           |                | Out            | puts           |                |

|--------|----------------|----------------|----------------|----------------|----------------|----------------|

| E      | A <sub>1</sub> | A <sub>0</sub> | Y <sub>3</sub> | Y <sub>2</sub> | Y <sub>1</sub> | Y <sub>0</sub> |

| 0      | Х              | Х              | 0              | 0              | 0              | 0              |

| 1      | 0              | 0              | 0              | 0              | 0              | 1              |

| 1      | 0              | 1              | 0              | 0              | 1              | 0              |

| 1      | 1              | 0              | 0              | 1              | 0              | 0              |

| 1      | 1              | 1              | 1              | 0              | 0              | 0              |

$From Truth table, we can write the {\it Boolean functions} for each output as$

### 3 to8Decoder

Let3to8Decoderhas3inputsA<sub>2</sub>A<sub>1</sub>&A<sub>0</sub>and8outputsY<sub>7</sub>,Y<sub>6</sub>,Y<sub>5</sub>,Y<sub>4</sub>,Y<sub>3</sub>,Y<sub>2</sub>,Y<sub>1</sub>&Y<sub>0</sub>. The **block diagram** of 3 to 8 decoder is shown in the following figure.

i.einputlines'n'=3

outputlines= $2^n=2^3=8$

| Enable | Ι              | nput  | s              | Outputs |    |            |                       |            |                |                |                       |

|--------|----------------|-------|----------------|---------|----|------------|-----------------------|------------|----------------|----------------|-----------------------|

| Е      | A <sub>3</sub> | $A_1$ | A <sub>0</sub> | Y7      | Y6 | <b>Y</b> 5 | <b>Y</b> <sub>4</sub> | <b>Y</b> 3 | Y <sub>2</sub> | $\mathbf{Y}_1$ | <b>Y</b> <sub>0</sub> |

| 0      | х              | х     | х              | 0       | 0  | 0          | 0                     | 0          | 0              | 0              | 0                     |

| 1      | 0              | 0     | 0              | 0       | 0  | 0          | 0                     | 0          | 0              | 0              | 1                     |

| 1      | 0              | 0     | 1              | 0       | 0  | 0          | 0                     | 0          | 0              | 1              | 0                     |

| 1      | 0              | 1     | 0              | 0       | 0  | 0          | 0                     | 0          | 1              | 0              | 0                     |

| 1      | 0              | 1     | 1              | 0       | 0  | 0          | 0                     | 1          | 0              | 0              | 0                     |

| 1      | 1              | 0     | 0              | 0       | 0  | 0          | 1                     | 0          | 0              | 0              | 0                     |

| 1      | 1              | 0     | 1              | 0       | 0  | 1          | 0                     | 0          | 0              | 0              | 0                     |

| 1      | 1              | 1     | 0              | 0       | 1  | 0          | 0                     | 0          | 0              | 0              | 0                     |

| 1      | 1              | 1     | 1              | 1       | 0  | 0          | 0                     | 0          | 0              | 0              | 0                     |

$From Truth table, we can write the {\it Boolean functions} for each output as$

$$Y_{0} = EA_{2} \qquad A_{1}$$

$$A_{0}Y_{1} = E \qquad A_{2} \qquad A_{1}$$

$$A_{0}Y_{2} = E \qquad A_{2} \qquad A_{1}$$

$$A_{0}Y_{2} = E \qquad A_{2} \qquad A_{1}$$

$$A_{0}Y_{3} = E \qquad A_{2} \qquad A_{1}$$

$$A_{0}Y_{4} = E \qquad A_{2} \qquad A_{1}$$

$$A_{0}Y_{5} = E \qquad A_{2} \qquad A_{1}$$

$$A_{0}Y_{6} = E \qquad A_{2} \qquad A_{1}$$

$$A_{0}Y_{7} = EA_{2}A_{1}A$$

0

Logical circuit of the above expression sis given below:

Logicdiagram3to8linedecoder

#### Encoder:

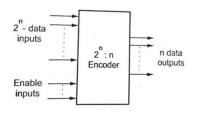

An encoder is a multiple input multi output combinational digital circuit that performs the inverse operation of a decoder. It means that an encoder converts the 2<sup>n</sup>number of coded inputs into n number of coded outputs.

The output lines of a digital encoder generate the binary equivalent of the input line whose value is equal to 1 and are available to encode either a decimal or hexadecimal input pattern to typically a binary or B.C.D (binary coded decimal) output code

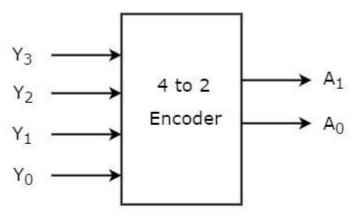

#### 4 to2lineEncoder:

There are four inputs (Y0, Y1, Y2, and Y3) and two outputs (A0 and A1) in the 4 to2lineencoder.Inaddition,Togettherespectivebinarycodeontheoutputside,one

inputlineatatimeissettotrueina4-inputline.The4to2lineencoder'sblock diagram and truth table are shown below.

|    | Inp            | Outputs |       |    |    |

|----|----------------|---------|-------|----|----|

| Y3 | Y <sub>2</sub> | $Y_1$   | $Y_0$ | A1 | Ao |

| 0  | 0              | 0       | 1     | 0  | 0  |

| 0  | 0              | 1       | 0     | 0  | 1  |

| 0  | 1              | 0       | 0     | 1  | 0  |

| 1  | 0              | 0       | 0     | 1  | 1  |

$The terms A_0 and A_1 are logically expressed as follows:$

$$A_1 = Y_3 + Y_2$$

$A_0 = Y_3 + Y_1$

#### **Circuit Diagram**

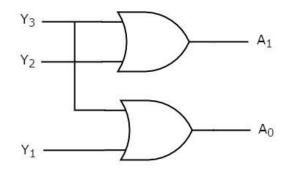

TwoinputORgatescanbeusedtoimplementtheaforementionedtwoBoolean functions. Further, The 4 to 2 encoder circuit diagram is given in the graphic below.

#### **Usesof Encoder**

Inalldigitalsystems, these systems are relatively simple to operate.

To convertade cimal number to a binary number, encoders are employed. The goalisto complete a binary operation like addition, subtraction, multiplication, and so on.

#### Disadvantages

The disadvantages of a standard encoder are listed below.

- Whenalloftheencoder'soutputsare0,there isambiguity.Becausewhenonlytheleast significantinputisoneorwhenallinputsarezero,itcouldbethecode inputs. n atchingthe

- Whenmorethanoneinputissettohigh,theencodergeneratesanoutputthatmayor maynotbethepropercode.IfbothY3andY6are'1',forexample,theecoder outputs 111.ThisisneitherthecomparablecodeforY3,whenitis'1',norisittheequivalent code for Y6, when it is '1'.

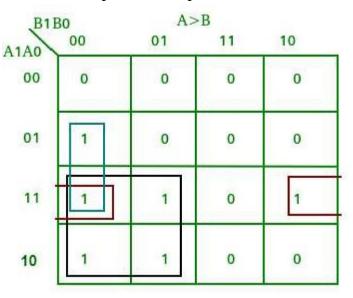

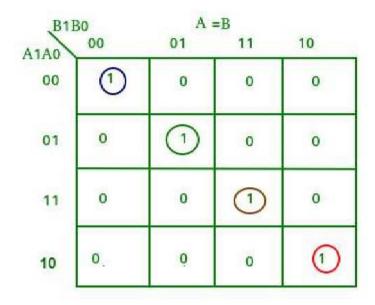

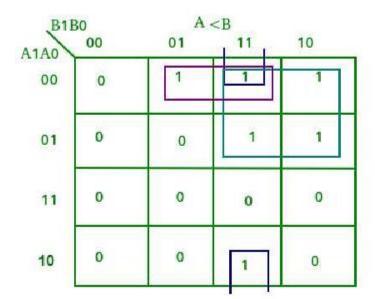

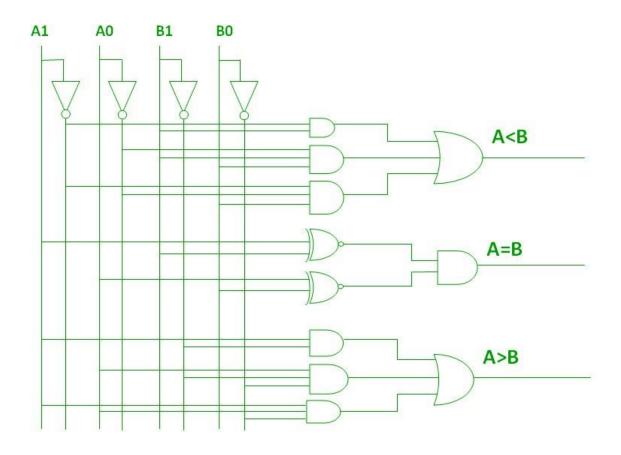

## WorkingofTwobitmagnitudecomparator.

AmagnitudedigitalComparatorisacombinationalcircuitthat**comparestwo digitalor binary numbers** in ordertofindoutwhetheronebinarynumber isequal,less than, or greater than the other binary number. We logically design a circuit for which we will have two inputs one for A and the other for B and have three output terminals, one for A > B condition, one for A = B condition, and one for A < B condition.

$$\begin{array}{c|c}

A & & & \\

N & - & bit \\

Comparator & & A = B \\

B & & & A < B

\end{array}$$

| Trutł | ntable |       |    |         |     |                   |

|-------|--------|-------|----|---------|-----|-------------------|

|       | Inj    | out   |    | Out put |     |                   |

| I     | 4      | ]     | В  | A>B     | A=B | A <b< td=""></b<> |

| A1    | A      | $B_1$ | Bo |         |     |                   |

| 0     | 0      | 0     | 0  | 0       | 1   | 0                 |

| 0     | 0      | 0     | 1  | 0       | 0   | 1                 |

| 0     | 0      | 1     | 0  | 0       | 0   | 1                 |

| 0     | 0      | 1     | 1  | 0       | 0   | 1                 |

| 0     | 1      | 0     | 0  | 1       | 0   | 0                 |

| 0     | 1      | 0     | 1  | 0       | 1   | 0                 |

| 0     | 1      | 1     | 0  | 0       | 0   | 1                 |

| 0 | 1 | 1 | 1 | 0 | 0 | 1 |

|---|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 1 | 0 |

From the above truth table K-map for each output can be drawn as follows:

$A > B = A_1 A_0 \overline{2}_0 + \overline{2}_1 \overline{2}_0 A_0 + A_1 \overline{2}_1$

$A=B = \overline{\mathbb{D}}_{1}\overline{\mathbb{D}}_{0}\overline{\mathbb{D}}_{1}\overline{\mathbb{D}}_{0} + \overline{\mathbb{D}}_{1}A_{0}\overline{\mathbb{D}}_{1}B_{0} + A_{1}A_{0}B_{1}B_{0} + A_{1}\overline{\mathbb{D}}_{0}B_{1}\overline{\mathbb{D}}_{0}$

$= (\mathbb{P}_{1}\overline{\mathbb{P}_{1}} (\mathbb{P}_{0}\overline{\mathbb{P}}_{0} + \mathbb{P}_{0}\mathbb{P}_{0}) + \mathbb{P}_{1}\mathbb{P}_{1}(\mathbb{P}_{0}\mathbb{P}_{0} + \mathbb{P}_{0}\overline{\mathbb{P}}_{0})$  $= (\mathbb{P}_{1}\overline{\mathbb{P}_{1}} + \mathbb{P}_{1}\mathbb{P}_{1})(\mathbb{P}_{0}\mathbb{P}_{0} + \mathbb{P}_{0}\overline{\mathbb{P}}_{0})$  $= (\mathbb{P}_{1} \odot \mathbb{P}_{1})(\mathbb{P}_{0} \odot \mathbb{P}_{0})$

$A{<}B = \boxed{2}_{1}\boxed{2}_{0}\boxed{2}_{1}{+}\boxed{2}_{1}\boxed{2}_{0}\boxed{2}_{0}{+}\boxed{2}_{1}\boxed{2}_{1}$

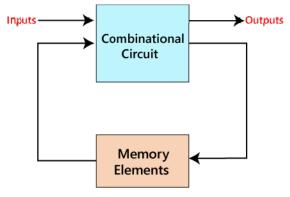

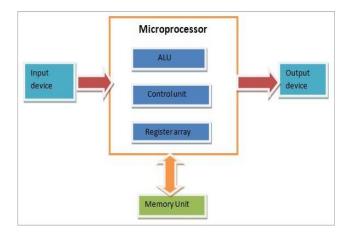

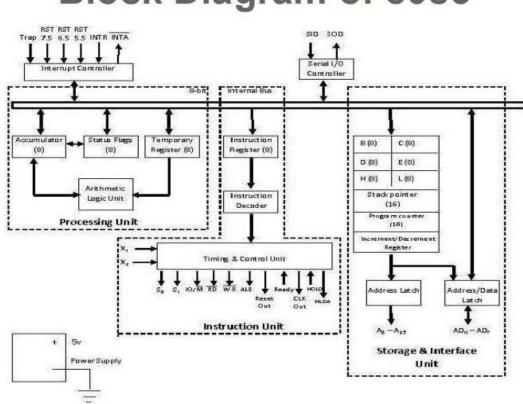

## **3.SEQUENTIALLOGIC CIRCUITS**

The outputs of the sequential circuits depend on both the combination of present inputs and previous outputs. The previous output is treated as the present state. So, the sequentialcircuitcontainsthecombinationalcircuitanditsmemory storageelements. A sequentialcircuitdoesn'tneedtoalwayscontainacombinational circuit.So, the sequential circuit can contain only the memory element.

BLOCKDIAGRAMOFSEQUENTIALCKT

Differencebetweenthecombinationalcircuitsandsequentialcircuitsaregiven below:

|   | CombinationalCircuits                | SequentialCircuits                      |  |  |

|---|--------------------------------------|-----------------------------------------|--|--|

| 1 | The outputs of the combinational     | Theoutputsofthesequentialcircuits       |  |  |

|   | circuitdependonlyonthepresent inputs | dependonboth presentinputsand           |  |  |

|   |                                      | present state(previous output).         |  |  |

| 2 | Thefeedbackpathisnotpresentinthe     | Thefeedbackpath ispresent in the        |  |  |

|   | combinationalcircuit.                | sequentialcircuits.                     |  |  |

| 3 | In combinational circuits, memory    | In the sequential circuit, memory       |  |  |

|   | elements are not required.           | elementsplayanimportantroleand          |  |  |

|   |                                      | require.                                |  |  |

| 4 | Theclocksignalisnotrequiredfor       | Theclocksignalisrequired for sequential |  |  |

|   | combinationalcircuits.               | circuits.                               |  |  |

| 5 | Thecombinationalcircuitissimpleto    | Itisnotsimpletodesignasequential        |  |  |

|   | design.                              | circuit.                                |  |  |

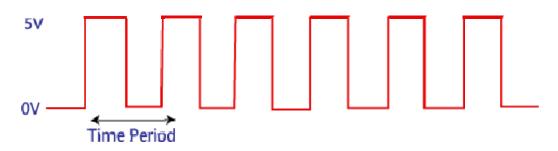

State the necessity of clock and give the concept of level clocking andedge triggering,

1.Clock:

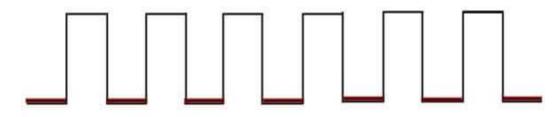

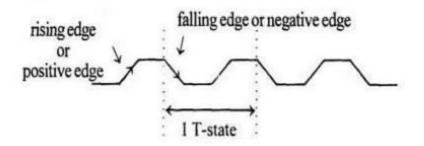

A clock signalis a periodic signalin whichON time and OFF time neednotbe the same.WhenONtimeandOFFtimeoftheclocksignal arethesame, a squarewaveisused torepresenttheclocksignal.Belowisa diagramwhich representstheclocksignal:

Aclocksignalisconsideredasthesquarewave.Sometimes,thesignal stays at logic, either high 5V or low 0V, to an equal amount of time. It repeats with a certain time period, which will be equal to twice the 'ON time' or 'OFF time'.

#### TypesofTriggering

Thesearetwotypesoftriggeringinsequential circuits:

#### Level triggering

ThelogicHighandlogicLo <sub>V</sub> arethetwolevelsintheclocksignal.Inleveltriggering, whentheclockpulseisata <sub>p</sub>articularlevel,onlythenthecircuitisacti ated.Thereare thefollowingtypesofleveltriggering:

#### Positivelevel triggering

In a positive level triggering, the signal with Logic High occurs. So, in this triggering, the circuit is operated with such type of clock signal. Below is the diagram of positive level triggering:

#### Negativelevel triggering

Innegativeleveltriggering, the signal with Logic Lowoccurs. So, in thit riggering, the circuit isoperated with such type of clock signal. Below is the diagram of Negative level triggering:

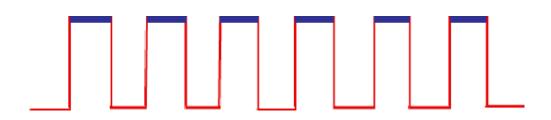

#### Edgetriggering

Inclocksignalofedgetriggering, two types of transitions occur, i.e., transitioneither from Logic Low to Logic High or Logic High to Logic Low.

Basedonthetransitions of the clock signal, there are the following types of edge triggering:

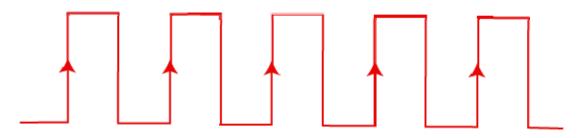

#### Positiveedge triggering

The transition from Logic Low to Logic High occurs in the clock signal of positive edge triggering.So,inpositiveedgetriggering,thecircuitisoperatedwithsuchtypeofclock signal.Thediagramofpositieedgetriggeringisgivenbelow.

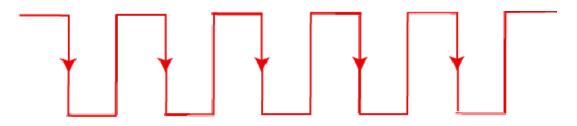

#### Negativeedge triggering

The transition from Logic Highto Logic low occurs in the clock signal of negative edge triggering. So, innegative edge triggering, the circuit is operated with such type of clock signal. The diagram of negative edge triggering is given below.

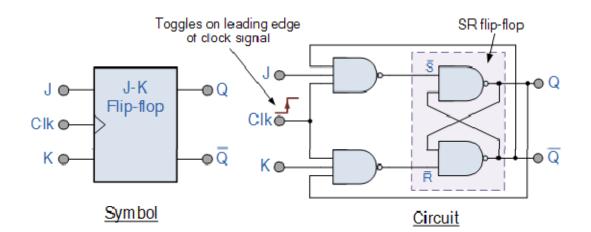

#### Whatisflipflop?

Flip-Flop is popularly known as the basic digital memory circuit. It is an edge triggered synchronoussequential logic circuit that is capable of storing single bit binary information. It has two states as logic 1(High) and logic 0(low) states. A flip flop is a sequential circuit which consists of a single binary state of information or data. The digital circuit is a flip flop which has two outputs and are of opposite states. It is also known as a Bistable Multivibrator.

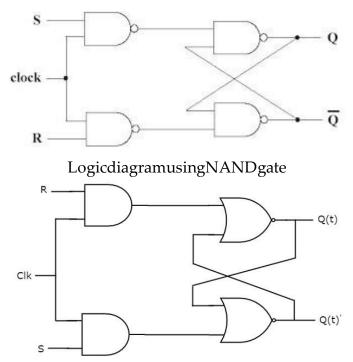

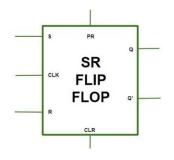

#### **ClockedSRflipflop**

SR(Set-Reset)flip-flopisaclockedsequentialcircuitwhichiscontrolledbyedge triggered CLK control signal.

LogicdiagramusingANDandNORgate Truth

| Γ | al | bl  | le |

|---|----|-----|----|

| - | ~  | ~ - | ~  |

|     | Inputs |   | Out | tputs | States    |  |  |

|-----|--------|---|-----|-------|-----------|--|--|

| CLK | S      | R | Q   | ?     |           |  |  |

| 0   | 0      | 0 | NC  | NC    | No.change |  |  |

| 0   | 0      | 1 | NC  | NC    | No.change |  |  |

| 0   | 1      | 0 | NC  | NC    | No.change |  |  |

| 0   | 1      | 1 | NC  | NC    | No.change |  |  |

| 1   | 0      | 0 | NC  | NC    | No.change |  |  |

| 1   | 0      | 1 | 0   | 1     | Reset     |  |  |

| 1   | 1      | 0 | 1   | 0     | Set       |  |  |

| 1   | 1      | 1 | Х   | Х     | No.change |  |  |

#### ClockedSRflipflopwithpresetandclearinputs.

In SR flip flop, with the help of Preset and Clear, when the power is switched ON, the state of the circuit keeps on changing, i.e. it is uncertain. It may come to Set(Q= 1) or Reset (Q' = 0) state. In many applications, it is desired to initially Set or Reset the flip flop. This thing is accomplished by the Preset (PR) and the Clear (CLR).

#### **BLOCKDIAGRAMOFF/F**

#### OperationsinSRFlip-Flop-

• Case-1:

PR=CLR=1

Theasynchronousinputs are inactive and the flip flop responds freely to the S, R and the CLK inputs in the normal way.

• Case-2:

PR=0andCLR=1

ThisisusedwhentheQissetto1.

#### • Case-3:

PR=1andCLR=0

This is used when the Q'issetto 1.

• Case-4:

PR=CLR=0

Thisisaninvalidstate.

|    | INPUTS |     |    |    |        | YUTS    | Comments  |

|----|--------|-----|----|----|--------|---------|-----------|

| PR | CLR    | CLK | S  | R  | Q(n+1) | ? (n+1) |           |

| 0  | 1      | NA  | NA | NA | 1      | 0       | Set       |

| 1  | 0      | NA  | NA | NA | 0      | 1       | Re-set    |

| 1  | 1      | 0   | NA | NA | Qn     | ? n     | No.change |

| 1 | 1 | 1 | 0 | 0 | Qn | ? n | No.change  |

|---|---|---|---|---|----|-----|------------|

| 1 | 1 | 1 | 1 | 0 | 1  | 0   | Set        |

| 1 | 1 | 1 | 0 | 1 | 0  | 1   | Re-set     |

| 1 | 1 | 1 | 1 | 1 | Х  | х   | Notallowed |

#### ApplicationsofFlip-Flop:

- 1. Flipflopsareusedasabounceeliminationswitch.

- 2. Theyareusedasaserialtoparallelandparalleltoserialconversion.